# Enhanced Fault Tolerant Parallel FFTs Using Parseval Checks and Error Correction Codes Using Ancient Indian Mathematics

Panjala Kranthi Kumar

PG Scholar, Electronics Design Technology, SR Engineering College, Warangal, Telangana, India

## P. Anuradha

Senior Assistant Professor, Department of Electronics and Communication Engineering, SR Engineering College, Warangal, Telangana, India

Abstract - The convolution in signal processing systems and communication circuits rises per annum. This can be attained using CMOS technology scaled down to a single device. Soft errors creates dependability hazard in recent circuit systems. Signal processing and communication system circuits aren't exclusion in the current advancement. In few utilizations, a possible activity is that use of algorithmic based fault tolerance (ABFT) approaches that are strive and deed of recursive attributes in recognize as well as rectify faults. Communications and Signal processing utilities are more compatible to algorithmic based fault tolerance. A few key building blocks in devices are FFTs. Many secured techniques suggested for recognize as well as rectify faults in FFTs. Amidst of techniques, most likely utilization of Sum of squares or parseval check is the most generally glorious. At a recent time, one method employs that put into effect of fault tolerance projected over similar filters. During irregularity, the system first implemented for lookout Fast Fourier Transforms. Later two more advanced security approaches are used by mixing for utilization of project and correct of parseval checks and error correction codes.

Index Terms - Fast Fourier Transforms, Error Correction Codes, Alogarithmic Based Fault Tolerance, Soft errors.

### 1. INTRODUCTION

Channels are ordinarily utilized as a part of electronic frameworks to underline motions in bound recurrence ranges and reject motions in elective recurrence ranges. In circuit hypothesis, a channel is relates electrical system that modifies the sufficiency as well as area attributes of an image with pertinence recurrence. In a perfect world, a channel won't add new frequencies to the information flag, nor would it be able to adjustment the part frequencies of that flag, notwithstanding it will alteration the relative amplitudes of the various recurrence components or potentially their area connections. These days channels zone unit wide utilized as a part of scope of utilizations that upheld car, restorative, and house wherever reliable of components in computerized electronic circuits is basic. Channels of some sort territory unit basic in the operation of most electronic circuits. There region unit a few entirely unexpected bases of ordering channels and these cover in a few distinctive courses; there is no clear hierarchal grouping. Since the behavioral properties of flag changes the strategies of sifting it'll be take issue. Being particular with channel, the computerized channels have huge applications in advanced flag process. Separating is moreover a classification of flag process, the procedure highlight of channels being the entire or incomplete concealment of some aspect of the flag. It's in this manner inside the enthusiasm of anybody worried in electronic circuit style to have the adaptability to create channel circuits fit for meeting a given arrangement of details. In flag process, an advanced channel is a gadget or process that evacuates some undesirable component or highlight from a sign. Computerized channels are utilized for to general purposes; partition of signs that are joined, and reclamation of signs that are mutilated in some approach. Frequently, this proposes evacuating a few frequencies and not others in order to stifle meddling signs and scale back foundation flag. This parallel operation is misused for adaptation to internal failure. Truth be told, dependableness might be a noteworthy test for electronic framework. in particular, delicate blunders are an essential issue, and loads of strategies are arranged throughout the years to moderate them. Some of these strategies alter the low-level style and usage of the coordinated circuits to prevent delicate blunders from happening. Distinctive strategies deal with the following deliberation level by including excess which will watch and appropriate blunders. The assurance of advanced channels has been wide examined. For example, blame tolerant executions upheld the usage of deposit assortment frameworks or math codes are arranged. The usage of diminished precision replication or word-level insurance has been moreover considered another decision to

ISSN: 2454-6410

perform mistake amendment is to utilize 2 totally unique channel executions in parallel. Every one of those procedures focus on the assurance of one channel.

Blunder coding is utilized for blame tolerant figuring in PC memory, attractive and optical data stockpiling media, satellite and part correspondences, arrange interchanges, PDA systems, and whatever other sort of advanced computerized correspondence. Blunder composing utilizes numerical recipes to code data bits at the source into longer piece words for transmission. The "code word" will then be decoded at the goal to recover the data. The extra bits inside the code word offer repetition that, in accordance with the composition subject utilized, will enable the goal to utilize the decoding technique to decide whether the correspondence medium presented blunders and at times amend them all together that the information needn't be retransmitted. Very surprising blunder composing plans are picked relying upon the sorts of mistakes expected, the correspondence medium's normal mistake rate, and regardless of whether or not data retransmission is attainable. faster processors and higher interchanges innovation make a great deal of complex coding plans, with higher blunder police work and adjusting capacities, achievable for littler inserted frameworks, permitting a ton of solid correspondences. Notwithstanding, tradeoffs between data measure and composing overhead, written work many-sided quality and permissible composition delay between transmissions, ought to be thought of for each application.

Various procedures is utilized to safeguard a circuit from mistakes. Those change from adjustments inside the creating strategy for the circuits to lessen the measure of mistakes to including excess at the rationale or framework level to ensure that blunders don't affect the framework reasonableness. Computerized Filters square measure one among the premier ordinarily utilized flag process circuits and various different strategies are anticipated to protect them from mistakes. There square measure scope of ways usual set up flaws and furthermore the activities important to remedy the deficiencies at interims circuit. Advanced channels square measure wide utilized as a part of flag process and correspondence frameworks. There square measure totally extraordinary adaptation to non-critical failure ways to deal with regular process circuits and furthermore the DSP circuits. Sometimes, the dependableness of these frameworks is crucial, and blame tolerant channel usage square measure required. Throughout the years, a few strategies that adventure the channels structure and properties to accomplish adaptation to noncritical failure are anticipated. By and large the systems said to this point, the insurance of one channel is considered.

Transient mistakes can frequently steamed more than one piece creating multi-bit blunders with a high likelihood of blunder event in neighboring memory cells. Bit interleaving is one procedure to cure multi-bit mistakes in neighboring memory cells as physically contiguous bits in memory cluster are appointed to various coherent words. The single-blunder adjustment, twofold mistake discovery, and twofold nearby blunder remedy (SEC-DED-DAEC) codes have already been introduced to rectify adjoining twofold piece blunders. The required number of check bits for the SECDED-DAEC codes is the same as that for the SEC-DED codes. What's more, the territory and timing overheads for encoder and decoder of the SEC-DED-DAEC codes are like those of the SEC-DED codes. Therefore, contiguous twofold piece mistakes can be cured with next to no extra cost utilizing the SECDED-DAEC codes. The SEC-DED-DAEC codes might be an alluring contrasting option to bit interleaving in giving more prominent adaptability to advancing the memory design. Besides, the SEC-DED-DAEC code can be utilized as a part of conjunction with bit interleaving and this technique can proficiently manage contiguous multi-bit mistakes. The FFTs in parallel builds the extent of applying blunder revision codes together. Producing equality together for parallel FFTs likewise helps in limiting the unpredictability in some ECC. By accepting that there must be a solitary mistake on the framework on account of radiation-instigated delicate blunders and might be two in most pessimistic scenario. The proposed new strategy depends on the mix of Partial Summation consolidated with equality FFT for different blunder redress.

## 2. LITERATURE SURVEY

[1]In this paper, adaptation to non-critical failure construct framework based with respect to Error Correction Codes (ECCs) utilizing Verilog is composed, actualized, and tried. It recommends that with the assistance of ECCs i.e. Mistake Correction Codes there will be more ensured Parallel channel circuit has been conceivable. The channel they have utilized for mistake location and revision are fundamentally limited impulse reaction (FIR) channels. They have been utilized Hamming Codes for blame adjustment in which they takes a piece of k bits and produces a square of n bits by including n–k equality check bits.

The equality check bits are XOR mixes of the k information bits. By legitimately planning those mixes it is conceivable to distinguish and amend blunders. In this plan they have utilized repetitive module in which the information and equality check bits are store d and can be recuperated later regardless of the possibility that there is a mistake in one of the bits. This is finished by re - figuring the equality check bits and contrasting the outcomes and the qualities put away. Along these lines utilizing hamming codes blunder can be recognized and adjusted inside the circuit.

[2] In this paper, Triple Modular Redundancy (TMR) and Hamming Codes have been utilized to secure distinctive circuits against Single Event Upsets (SEUs). In this paper, the utilization of a Novel Hamming approach on FIR Filters is examined and actualized to give low many-sided quality, decrease deferral and region productive security methods for higher bits information.

A novel Hamming code is proposed in this paper, to build the effectiveness of higher information bits. In this paper, they have proposed system used to illustrate, how the parcel of overhead because of scattering the repetition bits, their resulting expulsion, cushion to cushion postpone in the decoder and utilization of aggregate range of FIR channel for higher bits are lessened. These depend on the novel hamming code implementation in the FIR channel rather than traditional hamming code used to ensure FIR channel. In this plan Hamming code utilized for transmission of 7-bit information thing.

[3] In this paper, the outline of a FIR channel with self checking abilities in view of the buildup checking is dissected. Normally the arrangement of deposits used to check the consistency of the consequences of the FIR channel are based of theoretic contemplations about the dynamic range accessible with a picked set of buildups, the math attributes of the blunders caused by a blame and on the normal for the channel execution.

This investigation is regularly hard to perform and to acquire adequate blame scope the arrangement of picked buildups is overestimated. Acquired outcome and thusly requires that Instead, in this paper they have demonstrated how utilizing a thorough blame infusion crusades permits to proficiently choose the best arrangement of buildups.

Test comes about originating from blame infusion crusades on a 16 taps FIR channel exhibited that by observing the happened blunders and the location modules relating to various buildup has been conceivable to lessen the quantity of discovery module, while paying a little decrease of the level of SEUs that can be distinguished. Paired rationale rules the equipment execution of DSP frameworks

[4] In this paper they have proposed engineering for the execution of blame - tolerant calculation inside a high throughput multirate equalizer for a deviated remote LAN. The range overhead is limited by abusing the mathematical structure of the Modulus Replication Residue Number System (MRRNS). They had exhibited that for our framework the territory cost to redress a blame in a solitary computational

channel is 82.7%. Adaptation to internal failure inside MRRNS design is executed through the expansion of repetitive channels. This paper has introduced a nitty gritty investigation of the cost of actualizing single blame rectification capacity in a FIR channel utilizing the MRRNS. The blame tolerant design makes utilization of the arithmetical properties of the MRRNS, and has been appeared to give huge territory reserve funds when contrasted and general systems. This engineering likewise requires couple of extra parts to be outlined, as indistinguishable repetitive channels are utilized, and the polynomial mapping stages are basically extended from the first segments.

## 3. RELATED WORK

ERROR TOLERANT TECHNIQUES FOR PARALLEL FFTS:

2.1 Error Correction based on Hamming Codes:

The impulse response h[n] completely defines a discrete time filter that performs the following operation on the incoming signal x[n]:

$$y[n] = \sum_{l=0}^{\infty} x[n-l] \cdot h[l].$$

(1)

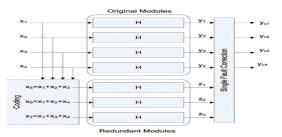

This property can be exploited in the case of parallel filters that operate on different incoming signals, as shown on Figure.1. In this case, four filters with the same response process the incoming signals  $x_1[n]$ ,  $x_2[n]$ ,  $x_3[n]$  and  $x_4[n]$  to produce four outputs  $y_1[n]$ ,  $y_2[n]$ ,  $y_3[n]$  and  $y_4[n]$ . To detect and correct errors, each filter can be viewed as a bit in an ECC, and redundant filters can be added to form parity check bits. This is also illustrated in Figure.1, where three redundant filters are used to form the parity check bits of a classical single error correction Hamming code. Those correspond to the outputs  $Z_1[n]$ ,  $Z_2[n]$  and  $Z_3[n]$ .

Errors can be detected by checking if

$$\begin{split} &Z_1[n] = y_1[n] + y_2[n] + y_3[n] \\ &Z_2[n] = y_1[n] + y_2[n] + y_4[n] \\ &Z_3[n] = y_1[n] + y_3[n] + y_4[n]. \end{split}$$

When some of those checks fail, an error is detected. The error can be corrected based on which specific checks failed. For example, an error on filter  $y_1$  will cause errors on the checks of  $Z_1$ ,  $Z_2$  and  $Z_3$ .

| C1<br>0 | $C_2$<br>0 | C <sub>3</sub><br>0 | Error Bit Position<br>No error |

|---------|------------|---------------------|--------------------------------|

| 1       | 1          | 1                   | $Z_1$                          |

| 1       | 1          | 0                   | $Z_2$                          |

| 1       | 0          | 1                   | $Z_3$                          |

| 0       | 1          | 1                   | $Z_4$                          |

| 1       | 0          | 0                   | $Z_5$                          |

| 0       | 1          | 0                   | Z <sub>6</sub>                 |

| 0       | 0          | 1                   | Z <sub>7</sub>                 |

|         |            |                     |                                |

Table 1: Error Location in the Hamming code

Figure 1 ECC-Based Scheme for Four Filters and a Hamming code.

The proposed schemes have been evaluated using FPGA implementations to assess the protection overhead. The results show that by combining the use of ECCs and Parseval Checks, the protection overhead can be reduced compared with the use of only ECCs.

2.2 Fault Tolerant FFT based on Parseval's check:

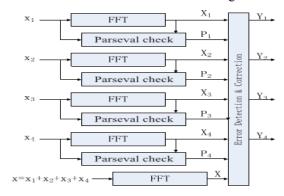

Parseval's technique is one amongst the techniques to detect errors parallel in multiple FFT. This is often achieved with sum of Squares (SOSs) check [5] supported Parseval's theorem. The error free FFT should have its sum of Squares of the input equaling the total of Squares of its frequency domain output. This correlation are often accustomed establish errors with minimum overhead. For parallel FFTs, the Parseval's Check is often combined with the error correction codes to attenuate the realm overhead. Multiple error detection and correction is achieved through this mix. One amongst the straightforward ways in which is to come up with the redundant input for single FFT with all the four FFT inputs. To correct error the parity FFT output is XORed with fault free outputs of the FFTs. Compared to the previous schemes bestowed within the Fault Tolerant Parallel FFTs victimization Error Correction Codes and Parseval Checks [1], this technique reduced the whole variety of sum of Squares used. Another existing work done is by combining SOS checks with hamming codes rather than exploitation Parseval's check on an individual as shown in Figure.2.

Figure 2 Parity-SOS (first technique) Fault-Tolerant Parallel FFTs.

This method combines the feature of parity calculation of hamming codes and error detection process of Sum of Squares. Concurrent Error Detection (CED) schemes for the FFT are the Sum of Squares (SOS) check based on Pa theorem. The use of parseval check is exponentially reduced to the direct comparisons of FFTs inputs and outputs used to protect parallel FFTs.

#### 4. PROPOSED MODELLING

The place to begin for our work is that the protection theme based on the utilization of ECCs that was for digital filters. This theme is shown in Fig1. In this example, a straightforward single error correction playacting code is employed. The initial system consists of 4 FFT modules and 3 redundant modules is value-added to sight and correct errors. The inputs to the 3 redundant modules area unit linear combos of the inputs and that they area unit used to check linear combos of the outputs. For example, the input to the primary redundant module is

$$x_5 = x_1 + x_2 + x_3.$$

And since the DFT is a linear operation, its output z5 can be used to check that

$$Z_5 = Z_1 + Z_2 + Z_3.$$

This will be denoted as c1 check. The same reasoning applies to the other two redundant modules that will provide checks c2 and c3. For example, for an error affecting z1, this can be done as follows:

$$Z_{1C}[n] = Z_5[n] - Z_2[n] - Z_3[n].$$

Similar correction equations can be used to correct errors on the other modules. More advanced ECCs can be used to correct errors on multiple modules if that is needed in a given application. For example, to protect four FFTs, three redundant FFTs are needed, but to protect eleven, the number of redundant FFTs in only four. This shows how the overhead decreases with the number of FFTs.

$$X_{1C} = X - X_2 - X_3 - X_4.$$

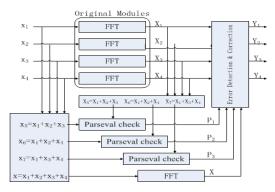

Another possibility to combine the SOS check and the ECC approach is instead of using an SOS check per FFT, use an ECC for the SOS checks. Then as in the parity-SOS scheme, an additional parity FFT is used to correct the errors. This second technique is shown in Figure 3.

Figure 3 Parity-SOS-ECC (second technique) Fault-Tolerant Parallel FFTs.

The main benefit over the first parity SOS scheme is to reduce the number of SOS checks needed. The error location process is the same as for the ECC scheme in Figure.1 and correction is as in the parity-SOS scheme. In the following, this scheme will be referred to as parity-SOS-ECC (or second proposed technique).

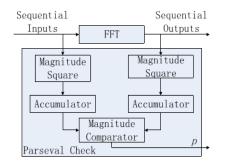

Figure 4 Implementation of the SOS check.

simulated and verified using Modelsim III 6.4b and synthesized using Xilinx ISE 13.2.

5. RESULTS AND DISCUSSIONS

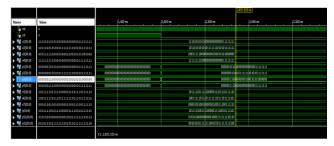

Simulation Result:

Figure 5: Simulation Result

Table 2: Design Summary

| Device Utilization Summary (Estimated Values) |      |           |             |  |  |

|-----------------------------------------------|------|-----------|-------------|--|--|

| Logic<br>Utilization                          | Used | Available | Utilization |  |  |

| Number of<br>Slices                           | 225  | 4656      | 4%          |  |  |

| Number of Slice<br>Flip Flops                 | 229  | 9312      | 2%          |  |  |

| Number of 4<br>input LUTs                     | 421  | 9312      | 4%          |  |  |

| Number of<br>bonded ICBs                      | 234  | 232       | 100%        |  |  |

| Number of<br>GCLKs                            | 1    | 24        | 4%          |  |  |

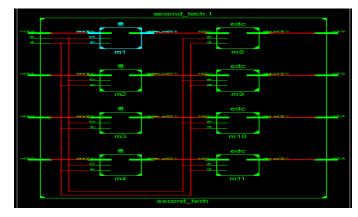

Figure 6: RTL Schematic

Figure 7: Technology Schematic

### Timing Report:

| Offset:<br>Source:<br>Destination:<br>Source Clock: | 4.040ns (<br>m8/data_2<br>y1<25> (P<br>clk risin | 6 (FF)<br>AD) | of Logic = 1) |                                                |  |

|-----------------------------------------------------|--------------------------------------------------|---------------|---------------|------------------------------------------------|--|

| Data Path: m8/data                                  | _26 to y1<                                       | 25>           |               |                                                |  |

|                                                     |                                                  | Gate          | Net           |                                                |  |

| Cell:in->out                                        | fanout                                           | Delay         | Delay         | Logical Name (Net Name)                        |  |

| FDR:C->Q                                            | 1                                                | 0.514         | 0.357         | m8/data 26 (m8/data 26)                        |  |

| OBUF:I->O                                           |                                                  | 3.169         |               | y1_25_OBUF (y1<25>)                            |  |

| Total                                               |                                                  | 4.040ns       |               | ns logic, 0.357ns route)<br>logic, 8.8% route) |  |

## 6. CONCLUSION

Detecting and correcting errors like important reliability are troublesome in signal process that will increase the utilization of fault tolerant implementation. In modern signal process circuits, it is common to search out many filters in operation in parallel. Proposed is a part economical technique to discover and correct single errors. The approach is based on applying SOS-ECC check to the parallel FFT outputs to discover and proper errors. The SOS checks are unit accustomed discover and find the errors and an easy parity FFT is employed for correction. The eight purpose FFT with the input bit length 32 is protected exploitation the planned technique. The detection and placement of the errors is done employing an SOS check per FFT or instead exploitation a set of SOS checks that type an error correcting code. This system will detect and proper only single bit error and it reduces space results in high speed compared to existing techniques.

#### REFERENCES

- Z. Gao 2015, "Fault tolerant parallel filters based on error correction codes. IEEE Transactions in Very Large Scale Integration(VLSI) Systems," 23(2): 384-387.

- [2] M. Nicolaidis. 2005, "Design for soft error mitigation," IEEE Transactions in Device Mater. Rel.5(3):405-418.

- [3] R. Baumann. 2005, "Soft errors in advanced computer systems," IEEE Des. Test Comput. 22(3):258-266.

- [4] N.Kanekawa, Ê.H.Ibe, T.Suga and Y. Uematsu. 2010, "Dependability in Electronic Systems: Mitigation of Hardware Failures, Soft Errors, and Electro-Magnetic Disturbances," New York, NY, USA: Springer-Verilag.

- [5] A. L. N. Reddy and P. Banerjee. 1990, "Algorithm based fault detection for signal processing applications," IEEE Transactions Computer. 39(10): 1304-1308.

- [6] P. Reviriego, S. Pontarelli, C. J. Bleakley and J. A.Maestro.2012, "Area efficient concurrent error detection and correction for parallel filters," IET Electron. Lett. 48(20): 1258-1260.

- [7] T.Hitana and A.K.Deb. 2004, "Bridging concurrent and non-concurrent error detection in FIR filters," in Proc. Norchip Conference pp. 75-78.

- [8] R. W. Hamming. 1950, "Error detecting and error correcting codes," Bell Systems Technology.29(2): 147-160.

- [9] E. P. Kim and N. R. Shanbhag. 2012, "Soft N-modular redundancy," IEEE Transactions Computer.61(3):323-336.

- [10] P. Reviriego, C. J. Bleakley and J. A. Maestro. 2012, "A novel concurrent error detection technique for the fast Fourier transform," in Proc.ISSC,Maynooth, Ireland. pp. 1-5.

- [11] [11]S. Pontarelli, G.C.Cardarilli, M. Re and A. Salsano. 2008, "Totally fault tolerant RNS based FIR filters," In Process 14th IEEE International On-Line Test Symp. (IOLTS). pp. 192-194.

Authors

**Panjala Kranthi Kumar** is pursuing Master of Technology in Electronic Design Technology in SR Engineering College, Warangal, Telangana. He has completed his B.Tech from Vaagdevi College of Engineering, Waranal, Telangana in 2015. His areas of interests are VLSI, Digital Signal Processing and Computer Networks. He Published 1 Poster in ICRTEECT-2017.

**P. Anuradha** working as Senior assistant professor of Electronics and Communication Engineering, S R Engineering College, Warangal. She has 12 years of teaching experience. She has obtained B.Tech (ECE) Degree from National Institute of Science Technology Warangal, Andhra Pradesh, India in 2003 and M.Tech (Embedded systems) Degree from JNTUH, Andhra Pradesh, India in 2010. Pursuing her Ph.D under JNTUH. She is a member of IETE, and her research areas include VLSI, Signal processing, and Embedded Systems.